產品介紹

概述

UC6580x-00是和芯星通研制的一款支持北斗三號的雙頻多系統亞米級定位精度SoC。這款基于22 nm工藝的低功耗、小型化射頻基帶一體化SoC具有抗多徑、抗干擾及高精度GNSS聯合定位技術,在功耗、尺寸敏感的場景下更勝一籌。

UC6580x-00面向全球應用,擁有96個跟蹤通道,支持GPS、GLONASS、北斗、Galileo、NavIC、QZSS,可多系統聯合定位,并支持多種SBAS信號接收處理,向用戶提供快速、準確的高性能定位體驗。

UC6580x-00支持L1 + L5/L2雙頻單點定位及RTD,并支持AGNSS功能。可用于可穿戴、手持設備、步行導航等領域,在城市多徑環境下相對于單頻方案明顯提升用戶體驗。

UC6580x-00芯片擁有車規級和工規級兩種規格,參見下表。

| 型號 | 等級 | 封裝 |

|---|---|---|

| UC6580A-00 | 車規級 | QFN40 |

| UC6580I-00 | 工規級 | QFN40 |

產品主要特性

基于22 nm工藝的小型化雙頻多系統GNSS SoC低功耗設計

兼容北斗三號的雙頻多系統并行捕獲、跟蹤技術,支持:

BDS B1I/B1C*+ B2a 或 B1I/B1C* + B2I

GPS L1 + L5 或 L1 + L2

Galileo E1 + E5a 或 E1 + E5b

GLONASS G1 或 G1+G2

QZSS L1 + L5 或 L1 + L2

SBAS L1

NAVIC L5*

實時寬窄帶抗干擾技術:帶內寬窄帶干擾檢測與移除,可抗總干擾功率不低于-75 dBm

支持L1 + L5/L2雙頻單點定位及亞米級RTD定位,具有優異的多徑抑制算法

超高靈敏度射頻與基帶設計:捕獲靈敏度優于-148 dBm,跟蹤靈敏度優于-162 dBm

支持AGNSS

支持安全啟動功能

擁有車規級和工規級兩種規格,采用QFN40封裝,詳見章節訂貨信息

UC6580A-00符合AEC-Q100 Grade2

*. 特定固件版本支持。 ?

技術指標

| 基本信息 | |||

| 通道 | 96通道 | ||

| 更新頻率 | 最大10 Hz | ||

| 數據格式 | NMEA-0183,Unicore,RTCM 3.xo | ||

| 頻點 | 模式一 | 模式二* | |

| BDS | B1I/B1C* + B2a | B1I/B1C* + B2I | |

| GPS | L1 + L5 | L1 + L2 | |

| Galileo | E1 + E5a | E1 + E5b | |

| GLONASS | G1 | G1 + G2 | |

| QZSS | L1 + L5 | L1 + L2 | |

| NavIC | L5* | - | |

| SBAS | L1 | L1 | |

| 觀測精度 | |||

| 水平位置精度(RMS) | 單點定位:1.5 m | ||

| 垂直位置精度(RMS) | 單點定位:2.5 m | ||

| 時間精度(RMS) | 5 ns,peak-to-peak value 30 ns (24h) | ||

| 速度精度1 | 0.02 m/s | ||

| TTFF2 | |||

| 冷啟動 | 26 s | ||

| 熱啟動 | 2 s | ||

| 重捕獲 | 1 s | ||

| 靈敏度3,4 | GNSS | ||

| 冷啟動 | -148 dBm | ||

| 熱啟動 | -156 dBm | ||

| 跟蹤 | -162 dBm | ||

| 重捕獲 | -159 dBm | ||

| 功耗(@25℃)5 | |||

| DCDC模式 | 捕獲: 40 mA @ 3 V | 跟蹤: 40 mA @ 3 V | |

| 備電模式 | 5 μA @ 3 V | ||

| 熱阻(@25℃) | |||

| ThetaJA | 44.96℃/W | ||

| ThetaJB | 11.48℃/W | ||

| 工作電壓 | |||

| 主電源 | 1.7 V ~ 3.6 V | ||

| IO電源 | 1.7 V ~ 3.6 V | ||

| 備電 | 1.7 V ~ 3.6 V | ||

| 通訊接口 | |||

| UARTⅹ2 | |||

| I2Cⅹ1 | |||

| SPI6ⅹ2 | |||

| 可靠性測試及認證 | |||

| 可靠性 | UC6580I-00 符合JESD47標準 | ||

| UC6580A-00符合AEC-Q100標準 | |||

| 認證 | 符合RoHS及REACH要求 | ||

o. 僅支持RTCM 3.x的消息輸入。 ?

*. 特定固件版本支持。 ?

1. 模擬器下-33 mps直線勻速運動場景。 ?

2. 衛星信號強度達到-130 dBm。 ?

3. 靈敏度指標需確保CN0為41 dB,性能可能會更新 ?

4. 外部匹配LNA以確保性能 ?

5. 與固件版本相關 ?

6. 當前固件暫不支持SPI接口 ?

引腳定義

引腳分布

UC6580A-00和UC6580I-00引腳分布相同,下圖以UC6580A-00為例進行介紹。

引腳說明

電源引腳說明

| 名稱 | 引腳 | 類型 | 描述 |

|---|---|---|---|

| DCDC_IN | 21 | Power | DC/DC供電輸入 (DCDC_IN和VDD_IO必須由同一個外部電源供電) |

| DCDC_OUT | 22 | Power | DC/DC供電輸出 |

| V_CORE | 23 | Power | Core供電輸入 |

| V_BACK | 6 | Power | 備份電源輸入 |

| VDD_IO | 7 | Power | IO/TCXO等供電輸入 (DCDC_IN和VDD_IO必須由同一個外部電源供電) |

| LDO_C | 24 | Power | Core LDO電壓輸出 |

| LDO_X | 2 | Power | TCXO LDO電壓輸出 |

| LDO_EX | 5 | Power | 僅供芯片自使用,不可對其他電路供電 |

| GND | 20 | - | 請接地 |

| V_DET1 | 8 | Power | 天線檢測供電輸入 |

| VDD_ANT | 9 | Power | 天線供電輸出 |

| LDO_RET | 10 | Power | 備份供電輸出 |

| GND | 地 |

1. 暫不支持天線檢測 ?

模擬引腳說明

| 名稱 | 引腳 | 類型 | 描述 |

|---|---|---|---|

| L1_IN | 40 | RF | L1 RF輸入 |

| L5_IN | 38 | RF | L5或L2 RF輸入 |

| TCXO_IN | 3 | Clock | 26 MHz TCXO輸入 |

| RTC_I | 12 | Clock | 32.768 kHz晶體或數字波形輸入 |

| RTC_O | 11 | Clock | 32.768 kHz時鐘輸出 |

| NC | 4 | - | 可以懸空或接地,建議接地 |

| NC | 39 | - | NC,請懸空 |

| NC | 1 | RF | NC,請懸空 |

PIO引腳說明

| 名稱 | 引腳 | 類型 | IO Reset | 描述 |

|---|---|---|---|---|

| PIO0 | 25 | IO | I/Pull-up | GPIO0 |

| PIO1 | 28 | IO | I/Pull-up | GPIO1 |

| PIO2 | 27 | IO | I/Pull-up | GPIO2 |

| PIO3 | 30 | IO | I/Pull-up | GPIO3 |

| PIO4 | 26 | IO | I/Pull-up | GPIO4 |

| PIO5 | 29 | IO | I/Pull-up | GPIO5 |

| TX | 19 | IO | I/Pull-up | GPIO6 |

| RX | 18 | IO | I/Pull-up | GPIO7 |

| SCL | 31 | IO | I/Pull-up | GPIO8 |

| SDA | 32 | IO | I/Pull-up | GPIO9 |

| D_SEL | 33 | IO | I/Pull-up | GPIO10 |

| PPS | 35 | IO | I/Pull-up | GPIO11 |

| BOOT_MODE | 34 | IO | I/Pull-up | GPIO12 |

| PIO13 | 14 | IO | I/Pull-up | GPIO13 |

| PIO14 | 13 | IO | I/Pull-up | GPIO14 |

| PIO15 | 36 | IO | I/Pull-up | GPIO15 |

| PIO16 | 37 | IO | I/Pull-up | GPIO16 |

| TMS | 16 | IO | I/Pull-up | GPIO17 |

| TCK | 15 | IO | I/Pull-up | GPIO18 |

| RESETN | 17 | IO | I/Pull-up | - |

芯片框架

芯片框圖

電源管理

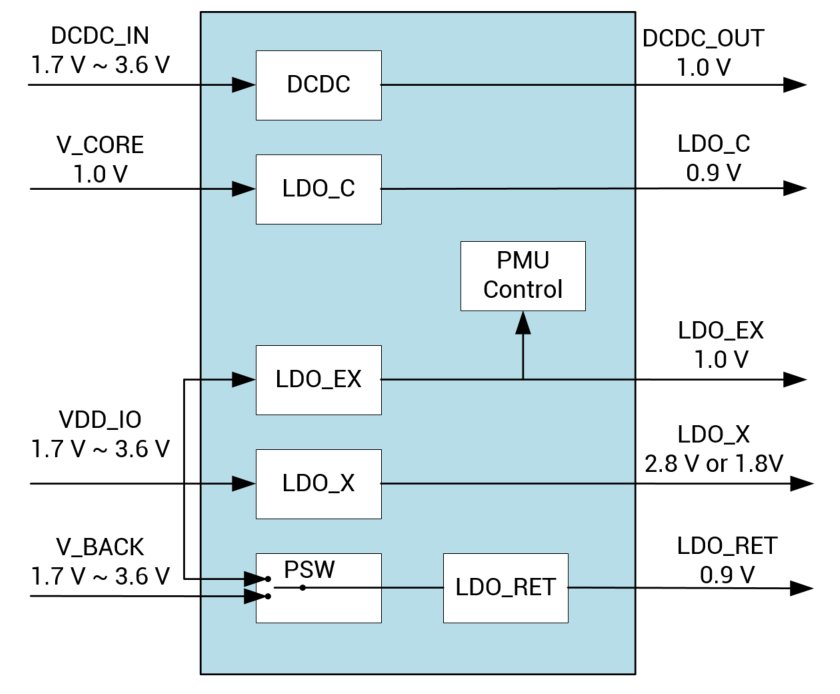

PMU提供四個電源域,由LDO內部生成并受幾個電壓監視器的監控。

Core電源域

Core電源域是芯片內RF和數字部分的主電源域,由V_CORE供電,V_CORE由LDO_EX或DCDC_OUT連接。后續的LDO_C轉換V_CORE輸入,將V_CORE轉換為各自電壓,并且須通過LDO_C引腳掛接去耦電容。LDO_C驅動數字邏輯部件。

IO電源域

IO電源域通過VDD_IO供電,包括芯片IO器件和片上Flash等。VDD_IO的供電電壓支持1.7 V ~ 3.6 V的寬壓。除了IO器件以外,PMU等設備由專用的LDO_EX供電。LDO_EX須通過LDO_EX引腳連接相應的去耦電容。

Backup電源域

Backup電源域包括RTC部分和Retention RAM。這個電源域由VDD_IO和V_BACK供電。當VDD_IO的供電電壓處于正常范圍時,使用VDD_IO,否則使用V_BACK。V_BACK的允許電壓范圍是1.7 V ~ 3.6 V。如果不需要RTC和backup功能,則V_BACK需要連接VDD_IO。

TCXO電源域

時鐘電源域,給TCXO供電。該電源域有一個專用LDO稱為LDO_X,也由VDD_IO供電。如果TCXO由LDO_X供電,LDO_X應連接到TCXO的電源引腳,同時用電容去耦。當然,用戶也可選擇除LDO_X以外的外部電源來使TCXO工作。

基于以上多電源域劃分及硬件設計,UC6580x-00芯片支持以下三種功耗模式:

工作模式(Running mode):芯片各電源供電正常,CPU正常運行,各電源域供電由軟件配置。所有事件,包括外部中斷、通訊請求、定時等事件都可以正常處理。

備電模式(V_BACK mode):外部切斷了芯片的IO供電和主供電,僅保留了V_BACK供電。此時芯片的功耗降到很低的水平,具體的功能和耗電依賴于軟件對此模式的設置;上電即醒。

斷電模式(Power Off mode):外部切斷了芯片的所有供電,芯片完全不工作。

芯片時鐘

系統需外部接入26 MHz時鐘,該時鐘由TCXO提供,為RF和基帶PLL提供參考頻率。為保證芯片啟動時PLL穩定工作,需要26 MHz時鐘在主電源和IO供電后10 ms內穩定工作。

系統支持RTC晶體輸入,RTC晶體通常由片內的32.768 kHz振蕩器驅動,該振蕩器需連接外部的32.768 kHz晶體。同時系統也支持RTC時鐘外部輸入,輸入信號幅度為0.9 V 至1.98 V,輸入信號頻率為32.768 kHz。兩種輸入方式二選一。RTC時鐘頻率偏差應小于20 ppm。

| 頻率源 | 頻率 | 備注 | |

|---|---|---|---|

| 系統時鐘 | TCXO | 26 MHz | 需在主電源和IO供電后10 ms內 穩定工作 |

| RTC時鐘 | 片內振蕩器 | 32.768 kHz | 芯片需外接32.768 kHz晶體 |

| 片外數字波形發生器 | 32.768 kHz | 輸入信號幅度為0.9 V ~ 1.98 V |

當主電源和IO供電掉電時,若V_BACK連接了備電,則基帶、RF、CPU均不再工作,而RTC仍保持運行為接收機提供守時參考,該工作模式即為RTC守時模式。RTC守時模式下,Retention RAM中仍保存相關數據用作GNSS熱啟動。

RTC守時模式對于GNSS熱啟動功能為必要前提,該模式下RTC提供時間信息,Retention RAM提供星歷、歷書等信息。如不使用GNSS熱啟動功能,RTC_O需接地。在基于AGNSS的系統中,若可通過網絡提供時間信息和星歷作為輔助,則RTC并非必需。

| 工作模式 | 供電 | |||||

| BB | RF | CPU | RTC | Retention RAM | ||

| RTC守時模式 | V_BACK | √ | √ | |||

芯片復位

按照UC6580x-00芯片的電源結構,有兩個復位域:Core域、Backup域。

Core 域有三種復位方式:

RESETN為芯片的復位引腳,當其電平為低,發出Core域復位信號,RESETN低電平持續時間應不小于5 ms。

芯片的軟件系統復位信號,由固件控制。

看門狗RESET。

上述復位源中的任何一個發出Core域復位信號,則Core域將被復位。

Backup域有兩種復位方式:

當V_BACK電壓低于1.2 V,則觸發復位。

軟件控制的RTC RESET信號,由固件控制,只復位RTC計數器。

RF子系統

UC6580x-00芯片射頻子系統實現了雙頻雙通道架構,輸入信號的頻率范圍為1166 MHz至1620 MHz。芯片接收到GNSS信號后,通過具有噪聲消除技術的單端低噪聲放大器(LNA)放大,然后送入射頻增益模塊進一步放大,從而降低了混頻級的噪聲系數要求。其中射頻增益模塊還提供單端到差分轉換。在完成正交下混頻轉換之后,多個GNSS信號被分成兩個通道。然后,分別對兩個通道的I和Q信號進行低通濾波,并通過單獨的可編程增益放大器(PGA)進行放大。再將兩個通道的I和Q信號發送到高速ADC部分進行數據轉換。

芯片射頻子系統支持以下任一種模式配置:

雙頻L1 + L5

雙頻L1 + L2

L1單頻多系統

LNA

LNA采用單級配置,需要外部匹配才能正常工作。建議增加外部LNA,以滿足高性能要求的應用場景,外部LNA增益范圍建議17 dB ~ 50 dB。在干擾復雜的環境下必需匹配外部SAW以抑制GNSS頻帶外的干擾。

射頻增益模塊

具備單端到差分轉換的射頻增益模塊位于內部LNA后面,提供進一步放大以及從單端到差分信號的轉換。

下混頻器

有源正交下混頻器首先將多路GNSS信號轉換至中頻信號,該階段信號經下變頻為兩路IF信號。

中頻低通濾波器

芯片內部集成I/Q低通濾波器,以濾除RF下變頻后的帶外噪聲,提高RF系統的噪聲性能。

AGC

芯片支持自動增益控制設計,收斂速度更快,計算成本更低。AGC增益控制單元依據RF系統所需的信號能量輸出增益配置字,以控制射頻數據鏈中各模塊的增益配置。

PGA及ADC

芯片內部集成PGA(可編程增益放大器)及高速ADC。PGA由AGC增益控制單元配置增益值,保證RF輸入信號能量在一定范圍內變化時輸出ADC的信號能量不變,從而保證高速ADC的輸出不致飽和。高速ADC支持I/Q復采樣信號輸出。

基帶子系統

UC6580x-00芯片提供多個接口用于數據通信或者外部設備的訪問,如UART,SPI,I2C,GPIO等。

本章將從下面幾個方面進行介紹:

接口

PIO復用說明

時間管理單元

看門狗

定時器計數器

接口

UART

芯片使用兩個UART接口:UART1和UART2。UART均可用于與主機通信。

UART1默認情況下,PIO6/PIO7對應UART1,在標準固件版本中作為主UART。通過BOOT_MODE可將UC6580x-00芯片的通信接口映射到不同的PIO接口。PIO6/PIO7也可被用作SPI,此時沒有UART1功能。關于BOOT_MODE使用及對應的通信接口映射請參見章節固件升級模式。

UART2可使用PIO15/PIO16,UART2主要用于輔助信息傳輸或調試。

SPI slave接口

芯片使用SPI slave接口作為與主機通信的可選方式來傳輸數據。同時支持由SPI slave接口加載固件。使用SPI slave的傳輸速率最大可支持8 Mbps,最大SPI時鐘頻率為8 MHz。但當SPI slave加載固件時,最大傳輸速率為4 Mbps。

SPI slave接口與UART1和I2C1分別復用引腳PIO6/PIO7和PIO8/PIO9,用戶可在啟動時使用D_SEL和BOOT_MODE來進行選擇。若PIO6/PIO7/PIO8/PIO9被用作SPI slave接口,則沒有UART1和I2C1功能;若PIO6/PIO7和PIO8/PIO9被分別用作UART1和I2C1,則沒有SPI slave接口。

當SPI slave接口用于主機通信時,PIO14應用作SRDY(Slave Ready)信號,用于表征SPI slave是否準備就緒。

SPI master接口

芯片提供SPI master接口,可以配置PIO0/PIO1/PIO4/PIO5為SPI master功能,用于與其他SPI slave設備通信或對其進行控制。SPI master接口的傳輸速率最大為16 Mbps,最大SPI時鐘頻率為16 MHz。

默認情況下SPI master接口未啟用。

I2C

芯片提供一個I2C接口(I2C1)用于固件加載及與主機進行通信。I2C1接口工作于slave模式。I2C協議和電氣接口兼容100 kbps、400 kbps和3.4 Mbps。當前固件僅支持400 kbps通訊。

默認情況下,I2C1接口使用PIO8/PIO9,BOOT_MODE應在啟動時處于上拉或開路狀態,詳情參見PIO復用說明。

I2C 時序要求

| 符號 | 參數 | 最小值 | 最大值 | 單位 |

|---|---|---|---|---|

| t_cycle | SCL時鐘周期 | 100 | 3400 | kbps |

| t_high | SCL時鐘高電平期間 | 0.06 | 5 | μs |

| t_low | SCL時鐘低電平期間 | 0.16 | 5 | μs |

| t_su | 數據建立時間 | 0.072 | μs | |

| t_hd | 數據保持時間 | 0.072 | μs | |

| t_s_su | 起始條件的建立時間 | 0.072 | μs | |

| t_s_hd | 起始條件的保持時間 | 0.072 | μs | |

| t_p_su | 停止條件的建立時間 | 0.072 | μs | |

| t_delay | 起始條件和停止條件之間的延時 | 0.5 | μs |

串行Flash接口

串行Flash接口用于芯片與外部SPI Flash的連接。SPI Flash可用于固件存儲及更新。

僅當BOOT_MODE在啟動時處于上拉或開路狀態時,串行Flash接口使用PIO0/PIO1/PIO2/PIO3/PIO4/PIO5;否則串行Flash接口無效。

PIO復用說明

PIO模塊可配置為GPIO,或作為前述通信接口。下表介紹所有PIO功能及復用情況。

| PIO # | 默認功能 | I/O | 說明 | 復用功能 |

|---|---|---|---|---|

| 0 | GPIO | I/O | - | SPI master MISO SPI flash D0 |

| 1 | GPIO | I/O | - | SPI master MOSI SPI flash D1 |

| 2 | GPIO | I/O | - | PWM0 UART2 RXD SPI flash WP |

| 3 | GPIO | I/O | - | PWM1 UART2 TXD SPI flash HOLD |

| 4 | GPIO | I/O | - | SPI master CLK SPI flash CLK |

| 5 | GPIO | I/O | - | SPI master CSN SPI flash CSN |

| 6 | GPIO | I/O | 啟動時,該引腳受BOOT_MODE控制: UART1 TXD(當BOOT_MODE在啟動 時為高) SPI slave MISO(當BOOT_MODE在 啟動時為低) | UART1 TXD SPI slave MISO |

| 7 | GPIO | I/O | 啟動時,該引腳受BOOT_MODE控制: UART1_RXD(當BOOT_MODE在啟動 時為高) SPI slave MOSI(當BOOT_MODE在 啟動時為低) | UART1 RXD SPI slave MOSI |

| 8 | GPIO | I/O | 啟動時,該引腳受BOOT_MODE控制: I2C1 SCL(當BOOT_MODE在啟動 時為高) SPI slave CLK(當BOOT_MODE在啟 動時為低) | I2C1 SCL SPI slave CLK |

| 9 | GPIO | I/O | 啟動時,該引腳受BOOT_MODE控制: I2C1 SDA(當BOOT_MODE在啟動時 為高) SPI slave CSN(當BOOT_MODE在 啟動時為低) | I2C1 SDA SPI slave CSN |

| 10 | GPIO | I/O | 通信接口選擇引腳。選擇通信接口位 于PIO6至PIO9。僅在啟動時有效。 此引腳如果留空,則被上拉。 | PPS D_SEL 32.768 kHz clock out |

| 11 | GPIO | I/O | - | PPS EVENT UART1 RXD |

| 12 | GPIO | I/O | 引導程序模式選擇引腳。 選擇固件加載地址,外部/內部Flash 或者SPI接口。僅在啟動時有效。 此引腳如果留空,則被上拉。 | BOOT MODE PPS RF_READY UART1 TXD |

| 13 | GPIO | I/O | ODO_DIR EVENT | |

| 14 | GPIO | I/O | - | ODO_CNT EVENT |

| 15 | GPIO | I/O | - | UART2 TXD LO1_DET |

| 16 | GPIO | I/O | - | UART2 RXD BLK LO2_DET |

| 17 | TMS | I/O | 調試接口 | ODO_DIR GPIO |

| 18 | TCK | I/O | 調試接口 | ODO_CNT GPIO |

I/O 復用部分修改詳細,請咨詢Unicore FAE。

時間管理單元

時間管理單元(TMU)管理基帶中的所有時鐘源,可以使用更精確的時鐘來校準不太精確的時鐘。

看門狗

UC6580x-00包含兩個看門狗定時器,防止在軟件陷入死鎖時導致系統閉鎖。在正常工作時,固件會在定時器發生溢出之前定期復位看門狗的內部計數器。

定時器計數器

定時器計數器有一個EVENT輸入和一個PPS輸出。

EVENT可以通過PIO11、PIO13或PIO14輸入,但同一時間只能輸入一個EVENT。EVENT輸入為相對于GPS時間的時間戳外部事件。

EVENT功能默認不支持,如有需求請聯系Unicore FAE。

PPS通過PIO11輸出。PPS輸出與GPS或UTC時間網格同步的脈沖序列,時間間隔可在很寬的頻率范圍內配置。

所有輸入和輸出信號均與接收機內部時鐘頻率同步,這使得輸入和輸出信號的固有最大量化誤差達到±10 ns級別。

系統配置

電源供電方案

UC6580x-00支持2種供電方案:內部DC-DC模式和LDO模式。

DCDC_IN和VDD_IO采用相同電源供電。

V_BACK可單獨供電,或者與DCDC_IN和VDD_IO采用相同電源供電。

TCXO供電使用LDO_X,電壓可選擇1.8 V或2.8 V1。

V_BACK供電電壓需不低于主電VDD_IO或在V_BACK供電電壓前加一個正向二極管防止VDD_IO給V_BACK倒灌電,同時V_BACK供電電壓需保證為1.7 V ~ 3.6 V,建議選用小功率(正向電流mA級即可)、正向壓降小(300 mV)、反向漏電流小(全溫度范圍內小于100 μA)的二極管。

如果不需要RTC和backup功能,則V_BACK需要連接VDD_IO。

DC-DC模式

在DC-DC模式下,主電(V_Main)接入DCDC_IN引腳,芯片的DC-DC模塊輸出DCDC_OUT給芯片其他部分提供電源供給,此時系統由內部DC-DC供電:

系統電源由DCDC_IN輸入,DCDC_OUT輸出經功率電感連接V_CORE輸入引腳。

LDO模式

在LDO模式下,主電(V_Main)接入DCDC_IN引腳,DCDC_IN與DCDC_OUT短接,芯片的DCDC模塊被旁路,直接由主電(V_Main)給芯片其他部分提供電源供給。此時:

DCDC_IN與DCDC_OUT短接在一起。

系統供電由 VDD_IO 輸入,經過 LDO_EX 輸出到 V_CORE, 由 LDO_EX 供電。

以上兩種模式的具體設計方法請參考《UC6580x-00硬件參考設計和注意事項》。

1. LDO_X輸出電壓在芯片出廠時確定,無法通過固件更改。當前量產出貨芯片輸出為1.8V,如需2.8V輸出,請提前聯系原廠。 ?

固件升級模式

UC6580x-00芯片通過D_SEL (PIO10) 和BOOT_MODE (PIO12) 引腳控制選擇固件升級模式,分為三種情形:

Mode 1:通過UART1或I2C1升級,此時UART1引腳為PIO6/7,I2C1引腳為PIO8/PIO9。

Mode 2:通過UART1升級,此時UART1引腳為PIO11/12。

Mode 3:通過SPI slave升級,此時SPI slave引腳為PIO6至PIO9。

芯片啟動時固件升級通信接口配置及升級模式說明參見下文。

BOOT_MODE僅在上電或RESETN被釋放之前有效。RESETN被釋放后,BOOT_MODE引腳可用作普通的PIO引腳。

固件升級啟動時管腳功能配置

| Mode | D_SEL | BOOT_ MODE |

Boot Mode |

說明 | |||

| PIO 6/7 | PIO 8/9 | PIO 11/12 | |||||

| Mode 1 | 1 | X | UART1和 I2C1啟動 |

UART1 | I2C1 | X | |

| Mode 2 | 0 | 1 | UART1 啟動 |

X | X | UART1 | UART1從 PIO11/ PIO12 啟動, 無I2C1啟動 |

| Mode 3 | 0 | 0 | SPI slave 啟動 |

SPI slave | SPI slave | X | |

這三種固件升級模式的啟動過程如下:

步驟1 CPU檢測接口的固件升級請求。

Mode 1升級模式

| If | Then |

|---|---|

| CPU在上電或復位后的40 ms內檢測到UART1的固件升級請求 | CPU開始自適應波特率并升級固件,升級完成后運行 |

| CPU在上電或復位后的40 ms內檢測到I2C1的固件升級請求 | CPU開始自適應I2C時鐘并升級固件,升級完成后運行 |

| CPU在上電或復位后的40 ms內同時檢測到UART1和I2C1的固件升級請求 | 優先初始化已識別波特率的接口,讀取該接口的升級請求,升級完成后運行 |

| CPU在上電或復位后的40 ms內未檢測到UART1或I2C1的固件升級請求 | 進行步驟2 |

Mode 2升級模式

| If | Then |

|---|---|

| CPU在上電或復位后的40 ms內檢測到UART1的固件升級請求 | CPU開始自適應波特率并升級固件,升級完成后運行 |

| CPU在上電或復位后的40 ms內未檢測到UART1的升級請求 | 進行步驟2 |

Mode 3升級模式

| If | Then |

|---|---|

| CPU在上電或復位后的40 ms內檢測到SPI slave接口的固件升級請求 | CPU升級固件,升級完成后運行 |

| CPU在上電或復位后的40 ms內未檢測到SPI slave接口的升級請求 | 進行步驟2 |

步驟2 CPU順序檢查封裝內嵌Flash以及外部Flash。

CPU檢測Flash

| If | Then |

|---|---|

| CPU檢測到封裝內嵌Flash中的固件 | 讀取內嵌Flash中的固件并運行 |

| CPU檢測到封裝內嵌Flash中無固件 | CPU嘗試讀取外部Flash中的固件,并運行。 |

電氣特性指標

本章介紹UC6580系列芯片的電氣特性指標。

其中,UC6580A-00的工作溫度為-40℃~105℃,UC6580I-00的工作溫度為-40℃~85℃。

以上溫度條件適用于本章所有電氣特性指標。

直流電氣特性指標

最大絕對額定值

| 符號 | 參數 | 最小值 | 最大值 | 單位 |

|---|---|---|---|---|

| DCDC_IN | 內部DC/DC轉換器輸入電壓 | -0.2 | 3.6 | V |

| DCDC_OUT | 內部DC/DC轉換器的輸出電壓, 外接電感及濾波電容,提供1.0V供電 建議電感值1uH,建議電容值10uF。 | -0.2 | 1.05 | V |

| VDD_IO | I/O,LDO_X和flash輸入電壓 | -0.2 | 3.6 | V |

| V_BACK | 備份域輸入電源電壓 | -0.2 | 3.6 | V |

| TCXO_IN | TCXO_IN上輸入電壓 | -0.6 | 2.9 | V |

| RTC_I | RTC_I上輸入電壓 | -0.2 | 1.98 | V |

| Vidig | PIO上輸入電壓 | -0.2 | 3.6 | V |

| Prfin | LNA_IN上RF輸入功率 | +15 | dBm | |

| Ptot | 總功率 | 360(常溫) | mW | |

| Tjun | 結溫 | -40 | +125 | °C |

| Ts | 儲存溫度 | -50 | +150 | °C |

所有輸入電壓,紋波均不能超過50 mV。

推薦工作條件

| 符號 | 參數 | 最小值 | 典型值 | 最大值 | 單位 |

|---|---|---|---|---|---|

| DCDC_IN | 內部DC/DC轉換器輸入電壓 | 1.7 | 3.3 | 3.6 | V |

| VDD_IO | I/O,LDO_X 和flash輸入電壓 | 1.7 | 3.3 | 3.6 | V |

| V_BACK | 備份域輸入電源電壓 | 1.7 | 3.3 | 3.6 | V |

PIO電氣特性指標

| 符號 | 參數 | 條件 | 最小值 | 典型值 | 最大值 | 單位 |

|---|---|---|---|---|---|---|

| Ileak | 輸入管腳 漏電 | 5 | μA | |||

| Vil | 允許輸入 的低電平 幅度 | 0.2×VDD_IO | V | |||

| Vih | 允許輸入 的高電平 幅度 | 0.8×VDD_IO | V | |||

| Vol | 輸出低電 平幅度 | Iout = -5mA | 0.4 | V | ||

| Voh | 輸出高電 平幅度 | Iout = 5mA | VDD_IO-0.55 | V | ||

| Rpu | 上拉電阻 | 200 | 260 | 320 | kΩ | |

| Cap_DIG_IN | 數字IO輸 入阻抗 | 0.7 | pF |

PIO輸出方式為推挽。

模擬電氣特性指標

模擬電氣特性指標1

| 符號 | 參數 | 最小值 | 典型值 | 最大值 | 單位 |

|---|---|---|---|---|---|

| LDO_X1 | LDO_X輸出電壓 (1.8 V TCXO) | 1.75 | 1.8 | 1.95 | V |

| LDO_X輸出電壓 (2.8 V/2.9 V TCXO) | 2.75 | 2.8 | 2.95 | V | |

| LDO_RET | LDO_RET輸出電壓 (VDD_IO 有電, V_BACK 有電) | 0.85 | 0.9 | 0.95 | V |

| LDO_RET輸出電壓 (VDD_IO 無電, V_BACK 有電) | 0.55 | 0.65 | 0.75 | V | |

| LDO_C | LDO_C 輸出電壓 | 0.85 | 0.9 | 0.95 | V |

| LDO_EX | LDO_EX輸出電壓 | 0.95 | 1.0 | 1.05 | V |

| V_DET2 | 天線檢測輸入 | 2.7 | 3.3 | 3.6 | V |

| VDD_ANT3 | 天線供電輸出 | 2.7 | 3.3 | 3.6 | V |

| RTC_I | 32.768 kHz晶體或 數字波形輸入 | 1.98 | V | ||

| RTC_O | 32.768 kHz時鐘輸出 | 1.98 | V | ||

| DCDC_OUT | 內部DC/DC轉換器的輸出電壓, 外接電感及濾波電容,提供1.0V供電。 建議電感值1uH,建議電容值10uF。 | 0.95 | 1.0 | 1.05 | V |

| TCXO_IN_Vpp | TCXO輸入峰-峰電壓 | 0.5 | 0.6 | 1.4 | Vpp |

1. LDO_X輸出電壓在芯片出廠時確定,無法通過固件更改。當前量產出貨芯片輸出為1.8V,如需2.8V輸出,請提前聯系原廠。 ?

2. 暫不支持天線檢測 ?

3. VDD_ANT輸出電壓為V_DET – (天線電流) × (10 Ω)。 ?

模擬電氣特性指標2 - RTC指標要求

| 符號 | 參數 | 條件 | 最小值 | 典型值 | 最大值 | 單位 |

|---|---|---|---|---|---|---|

| RTC_Fxtal | RTC晶振共振 頻率 | 32768 | Hz | |||

| RTC_T_start | RTC啟動時間 | 0.2 | 1 | 2 | s | |

| RTC_CL | RTC負載電容 | ESR = 80 kΩ | 12.5 | pF | ||

| RTC_Vil | RTC低電平輸 入電壓 | 共用RTC振蕩 器輸入 | 0.0 | 0.2 | V | |

| RTC_Vih | RTC高電平輸 入電壓 | 共用RTC振蕩 器輸入 | 0.9 | 1.98 | V |

RF電氣特性指標

| 符號 | 參數 | 條件 | 最小值 | 典型值 | 最大值 | 單位 |

|---|---|---|---|---|---|---|

| L1_IN | 接收機輸 入頻率 | 1559.098 | 1575.42 | 1606 | MHz | |

| L5_IN | 接收機輸 入頻率 | 1166.45 | 1176.45 | 1217.14 | MHz | |

| LNA_IN | LNA輸入 阻抗 | 需要匹配 器件和 隔直電容 | 50 | Ω | ||

| LNA_S11 | LNA輸入 回波損耗 | 50 Ω環境 | -10 | dB | ||

| NFtot | 接收機級 聯噪聲系 數 | 50 Ω環境 | 5 | dB | ||

| Ext_Gain | 外部LNA 增益 | 50 Ω環境 | 15 | 17 | 60* | dB |

| TCXO_Freq | TCXO 頻 率 | 0.5 ppm | 26 | MHz |

*. 外部LNA增益在該范圍時,系統CN0波動1 dB。 ?

機械尺寸

UC6580A-00 (QFN40車規)

UC6580I-00 (QFN40工規)

焊接要求

焊接要求

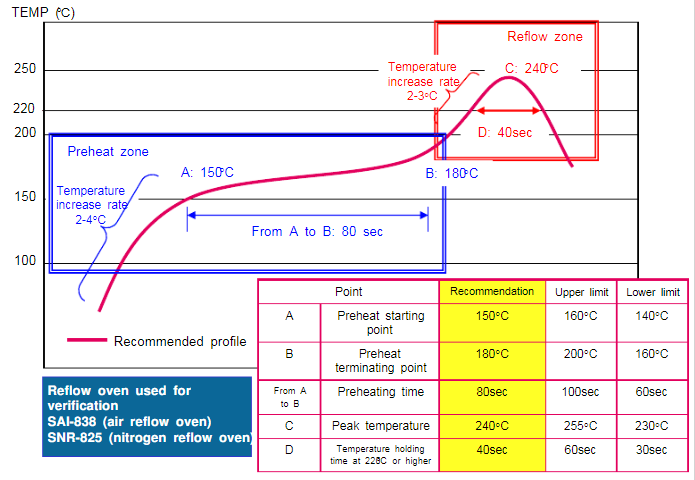

回流焊溫度曲線建議采用如下圖所示(錫膏建議使用M705-GRN360)。

產品外觀及包裝

外觀

UC6580A-00(QFN40車規) |

UC6580I-00(QFN40工規) |

標識

| 型號 | 說明 |

|---|---|

| UC6580A-00 | 級別-車規級(Automotive) |

| UC6580I-00 | 級別-工規級(Industrial) |

濕度敏感等級

UC6580A和UC6580I的濕度敏感等級如下表所示,與濕敏等級相關的包裝及操作注意事項參照標準 IPC/JEDEC J-STD-033。了解更多信息,可訪問JEDEC網站。

| 型號 | 濕度敏感等級 |

|---|---|

| UC6580A-00 | MSL 1 |

| UC6580I-00 | MSL 3 |

訂貨信息

| 型號 | 封裝 | 內置Flash | 工作溫度 | 等級 | 包裝 |

|---|---|---|---|---|---|

| UC6580A-00 | QFN40 5 mm × 5 mm × 0.85mm | Yes | -40 °C ~ 105 °C | 車規級 | 卷帶包裝, 每卷3000片 |

| UC6580I-00 | QFN40 5 mm × 5 mm × 0.85mm | Yes | -40 °C ~ 85 °C | 工規級 | 卷帶包裝, 每卷3000片 |